# Formal Methods for the Specification and Design of Real-Time Safety Critical Systems\*

Jonathan S. Ostroff

April, 1992

### Abstract

Safety critical computers increasingly affect nearly every aspect of our lives. Computers control the planes we fly on, monitor our health in hospitals and do our work in hazardous environments. Computers with software deficiencies that fail to meet stringent timing constraints have resulted in catastrophic failures. This paper surveys formal methods for specifying, designing and verifying real-time systems, so as to improve their safety and reliability.

<sup>\*</sup>To appear in *Journal of Systems and Software*, Vol. 18, Number 1, pages 33-60, April 1992. Jonathan Ostroff is with the Department of Computer Science, York University 4700 Keele Street, North York, Ontario, Canada, M3J 1P3. This work is supported by the Natural Sciences and Engineering Research Council of Canada.

#### Contents 1 Introduction $\mathbf{2}$ Defining the terms Major issues that formal theories must address . . . . . 2.13 **Real-Time Programming Languages** Structured Methods and/or Graphical Languages 4 4.1Structured Methods 4.2Graphical Languages with a formally defined semantics . . 4.2.1Statecharts and synchronous languages: . . . . . . 4.2.25 Logics and Algebras 5.1The TTM/RTTL framework — explicit clock linear 5.1.1MTL — hidden clock linear logics and other RTTL 5.1.25.1.3Branching time temporal logics . . . . . . . . . . 5.1.4Interval and other temporal logics . . . . . . . . Process Algebras 5.25.2.1UPA — Untimed Process Algebras . . . . . . . . 5.2.2TPA — Timed Process Algebras . . . . . . . . . . . RTL — Real Time Logic and Event Action Models . . . . 5.35.4Assertional and other formal methods . . . . . . . . . . . . . 5.4.1Real-Time Hoare Logic Putting Time into Proof Outlines . . . . . . . . . 5.4.2Hybrid Models 5.5

### 6 Future trends

$\mathbf{54}$

3

6

13

14

15

15

16

16

17

$\mathbf{21}$

24

26

32

36

38

39

39

42

48

50

50

51

52

# 1 Introduction

Computers are increasingly used to monitor and control safety critical systems. Real-time software controls aircraft, shuts down nuclear power reactors in emergencies, keeps telephone networks running, and monitors hospital patients. The use of computers in such systems offers considerable benefits, but also poses serious risks to life and the environment.

Safety critical systems must satisfy real-time constraints if they are to effectively perform their intended function. The newsletter *Software Engineering Notes* regularly reports incidents involving malfunctioning of real-time or embedded computer systems. For example, the first flight of the space shuttle was delayed by a subtle timing error, which was traced to an improbable race condition in the flight control software [31]. In another incident, a software error caused a stationary robot to move suddenly with impressive speed, to the edge of its operational area. A nearby worker was crushed to death. The firing mechanism of an already deployed ballistic missile system was recently analyzed using methods discussed in this survey. It was discovered that a certain sequence of events, unknown to the design team, would lead to the inadvertent firing of a missile [40].

Real-time software must satisfy not only functional correctness requirements, but also timeliness requirements. For example, consider the following "hard" real-time constraints: if the temperature of a nuclear reactor core is too high an alarm must be generated within some deadline; spray painting a car on a moving conveyor must be initiated at some suitable time and terminated some time later; when an aircraft enters an air traffic control region, the flight controller must be informed in a timely fashion; once the approach of a train is detected, car and pedestrian traffic at the train intersection must be halted before the train reaches the intersection; if the computer controlling a robot does not command it to stop or turn in time, the robot might collide with another object on the factory floor.

There is general consensus in the software and control systems literature that real-time systems are difficult to model, specify and design [142,42,17, 121,74,137,73]. In addition, experience has shown that software components of systems are problematic perhaps even more so than mechanical or other hardware components.

Software is complex (consider the documentation needed for even simple modules), non-robust (small errors have major consequences) and software

### 1 INTRODUCTION

is notoriously difficult to test (the number of test cases that must be checked becomes unmanageably large even in small systems) [115].

This does not necessarily mean that the software controlling real-time systems is poorly designed. Many companies do as much as is commercially feasible with current design methods to make their products more reliable. However, as the burden of controlling complicated systems is shifted onto the computer, so does the complexity of the resulting software increase. Old-fashioned servo-control systems could be tested in isolation. The new more complex software controllers are more difficult to check exhaustively, no matter how intelligently designed the test suite is.

It has been conjectured that formal, mathematically precise methods should be used to design real-time safety-critical systems. Turning this conjecture into sound practice has proved to be extremely difficult — many practically-oriented software engineers will probably consider the conjecture to face insurmountable hurdles.

But what benefits do "theorists" hope to obtain by the use of a formal framework? A list of the benefits includes:

- In the process of formalizing informal requirements, ambiguities, omissions and contradictions will often be discovered.

- The formal model may lead to hierarchical semi-automated (or even automated) system development methods.

- The formal model can be verified for correctness by mathematical methods (rather than by intractable case by case testing).

- A formally verified subsystem can be incorporated into a larger system with greater confidence that it behaves as specified.

- Different designs can be evaluated and compared.

Some researchers think that a specific real-time verification methodology is not needed. Conventional wisdom dictates that programs should be designed to function correctly, independent of hardware speed. One extreme position [138] views introducing time with grave suspicion. Time may be an issue in implementation ("use a faster machine if you miss the deadline") but should never appear in a specification. Furthermore, there

### 1 INTRODUCTION

is a danger in overspecifying and making the verification task more complex than it ought to be. In contrast, de Roever [22] considers it essential that foundational research be undertaken into formal methods for real time systems if reliable and safe systems are to be constructed.

If the designer is dealing with fixed schedules on a single processor, then it may be possible to get away with using untimed standard verification methods. Certainly one should abstract out time and use standard techniques wherever it is possible to do so. However, the work discussed in this survey clearly shows that tampering with the speed of the computer will not solve the main problems facing the designers of real-time software.

Time is not just another programming variable. Time is continuous, monotonic and divergent whereas program variables generally do not have such properties. Since time ranges over an infinite domain, all the tools that have been developed for finite state verification cannot be naively applied to real-time systems. With some effort, finite state methods can be made to work for real-time systems, but to do this certainly requires the adoption of specific formalisms to deal with explicit timing constraints. Proof systems for dealing with untimed infinite state systems must be refined if they are to deal safely with timed systems.

If time dependencies are introduced into a design, then there should be good reasons to do so. Mok [92] cites the following cases in which timing constraints play an important role.

- The control surfaces of some modern aircraft must be adjusted at a high rate to prevent catastrophic destruction. This places an upper bound on the response time of the avionics software system. Lower bounds are needed in operating systems which require a potential intruder to wait for some minimum time before retyping a password that has been entered incorrectly. In these cases, the "physics" of the application dictates the timing requirements.

- In the Byzantine Generals Problem, the non-faulty processors (generals) must arrive at a consensus to perform some action in the presence of other processors that can exhibit faulty behaviour. There is no asynchronous solution to the Byzantine Generals Problem. However, a solution is possible if the generals adopt the synchronous protocol of voting in rounds. In each round of voting the generals must complete

a set of communication actions within a real-time deadline. Thus, time is an essential synchronization mechanism for solving certain task coordination problems.

• In the NETBLT protocol proposed by a group at MIT, the receiver guarantees the sender that it will be able to process incoming packets at a certain rate, or alternatively, it will meet the deadline associated with each packet. Since the sender does not need to wait for an acknowledgment from the receiver, network throughput can be significantly improved, especially for networks where the round-trip transmission time is long compared with the width of a packet (e.g. in fiber optics communication systems). Thus, time is a control mechanism which can be exploited to solve problems more efficiently.

In the rest of this survey, we define more carefully what a real-time system is (Section 2). Three increasingly formal techniques are surveyed for dealing with real-time systems.

- Section 3 discusses real-time programming languages.

- Section 4 discusses structured analysis methods and graphical or visual modelling languages.

- Section 5 discusses logics and algebras.

Section 6 speculates on future trends.

## 2 Defining the terms

This section describes the important features of real-time systems. The following problems are also posed: the modelling problem, the verification problem, the design development problem and the controller synthesis problem. These are some of the main problems that theorists hope to tackle with formal methods.

An algorithm is usually represented as a *program*. Correctness of the algorithm means that the program *satisfies* some desired *specification* (or property). Therefore, in standard program verification, three concepts are needed. A programming language is needed for representing algorithms,

a specification language for expressing properties, and a satisfaction relation (or proof system) for verifying the correctness of the algorithm. An important subjective issue revolves around the choice of *syntax* for the programming and specification languages — does the syntax simplify the expression of algorithms and specifications, or does it get in the way of the designer.

To properly develop the concepts mentioned above, some additional notions must be introduced. A formal *semantics* must be provided so that the behaviour of the program and the meaning of the specifications are clearly defined. The proof system must be shown to be *sound* with respect to the semantics, so that only those programs whose behaviours satisfy the specification can be proven correct. An unsound proof system is dangerous because it can be used to prove anything (papers on the assignment axiom for arrays were, for years, filled with errors). Furthermore, it is useful if the proof system is *complete* so that every correct program can be verified for correctness in the proof system. Other issues such as the expressiveness of the languages and the complexity of decision procedures must be explored.

An algorithm usually takes some data as input, performs a computation and outputs the result of the computation to the user. For real-time programs, the situation is more complex. The environment in which the program operates can no longer be ignored, because of the intensive nonterminating interaction of the program with its environment. Such systems are often called embedded systems, discrete event dynamic systems, reactive systems, or process control systems. We shall refer to all of these as "real-time systems".

Ordinary programming languages are not expressive enough to represent the complex features of real-time systems such as concurrency, nondeterminism, synchronization between processes and real-time constraints on the events of such systems. Programming languages must therefore be extended if they are to deal with real-time systems. A *model* of the intended real-time notions is therefore needed.

A model is a representation, often in mathematical terms, of the important features of the system that is being studied. A common modelling technique is to define the *state* of the system (a "snapshot" at an instant in time of all the variables defining the system). A state may persist for some period of time, after which there is some change to a new state (as real-time systems are dynamic). Such a state change is referred to as an *event*

or a transition. The model may be used to simulate possible behaviours of the system which helps the designer understand the system better. A simulation of the system is a sequence of states and events capturing the behaviour of the system. A simulation may show the presence of bugs in the system, but never their absence [23]. Analysis of the system behaviour must be undertaken to show the correctness of the system. The system is correct provided that its behaviour satisfies the associated specification.

The terms "model" and "specification" are often used interchangeably. In this survey, a *model* is a *description* of the system, perhaps in great detail, or perhaps at a more abstract level. A *specification* is the list of *requirements* that the system must ideally satisfy. A model describes how the system actually behaves. A specification prescribes how we would like it to behave.

What are the most important features of a real-time system? The Oxford Dictionary of Computing defines a real-time system as follows:

[A real-time system is] any system in which the time at which the output is produced is significant. This is usually because the input corresponds to some movement in the physical world, and the output has to relate to that same movement. The lag from input time to output time must be sufficiently small for acceptable timeliness.

The IEEE Standard Dictionary of Electrical and Electronic Terms (Wiley 1978) gives the following definition:

*Real-Time:* (A) Pertaining to the actual time during which a physical process transpires. (B) Pertaining to the performance of a computation during the actual time that the related physical process transpires in order that results of the computation can be used in guiding the physical process.

In software engineering, the term "real-time system" usually refers to the software or programming code (called the *controller* in this survey). The lag time from input to output in the controller must be sufficiently small. However, there is implicitly always another object that is associated with the controller. That object is the physical world or environment in which the controller finds itself. Since the environment is always implicitly

### 2 DEFINING THE TERMS

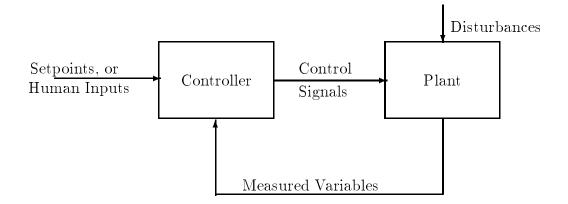

there, let us give it a name and call it the *plant*. Then we can refer to the plant and perhaps even reason about it. In fact, the lag time or response time of the controller is determined by the physical nature of the processes in the plant. The primary goal of the designer is to ensure the correct behaviour of the plant. This is achieved by designing a controller that will interact and control the plant. We may draw an automatic control diagram that is familiar to control engineers:

The complete system under development (SUD) is divided into two parts: the controller and the plant. The plant is that part of the system that is to be controlled. It is often a physical or technological process such as a chemical reaction, airplane or robot. The plant is usually a "given"; the designer is not free to change it, although there is usually some kind of "control technology" through which the plant can be controlled (e.g. control valves can be opened or certain plant events can be forced to occur through interlocks). The "open-loop" behaviour of the plant (without the controller) is usually unsatisfactory in some important respect.

It is the task of the controller to ensure that unsatisfactory behaviour in the plant is eliminated. The diagram above indicates the role that feedback plays in the controller. Feedback restores equilibrium after disruptions caused by disturbances to the plant. After measuring the current state of the plant the controller can take corrective action by issuing appropriate control commands.

### 2 DEFINING THE TERMS

There is usually much more freedom in the design of the controller than in that of the plant. In fact, the controller is often implemented by real-time software precisely so that the logic of the controller, or the computation that it performs, can easily be changed if necessary. As a result, the design of a real-time system differs from straight programming (e.g. coding an algorithm) in two important respects:

1. The plant is part of the overall system. A real-time system is one in which the *controller* software must synchronize with the *plant* processes whose progress it cannot directly control, so as to ensure that the plant behaves safely and reliably.

The design formalism must be flexible enough to represent the plant as an integral part of the complete system. Unsatisfactory plant behaviour can then be examined, and the effect of different control policies on the plant can be evaluated. Potential failures of the plant must be represented in the plant model so that the controller can be checked to see that it functions correctly. A model of the plant will enable the designer to extract the lag and real-time response times that the controller must implement. Furthermore, a deterministic formalism developed for a real-time programming language (to guarantee predictable behaviour), may be unsuitable for representing nondeterministic and asynchronous event driven plant behavior.

2. The plant must be verified for correctness. The essential concern of the designer is to ensure that the plant behaves in a safe, acceptable fashion. The correctness of the control software is only a means for ensuring correct plant behaviour. If the software of the controller fails (relative to its local specification) in a fashion that has no impact on the plant, then no harm has been done. By contrast, the controller can satisfy all kinds of requirement specifications, but if those requirements do not translate into proper behaviour of the plant, then the verification effort will have been in vain. An important corollary is that a specification of the system must primarily refer to the states, events and properties of the plant (not to the behaviour of the controller software).

Consider the following robot example<sup>1</sup>. The system under development

<sup>&</sup>lt;sup>1</sup>The robot example was used in a discussion on real-time issues on Usenet in 1990 with

(SUD) is a robot arm together with position sensors, a force sensor, a camera, a tactile sensor, a gripper, a joystick and keyboard for input, and a computer to control the various parts. Formally, we may write

### $SUD = plant \| controller$

where  $\parallel$  indicates the parallel composition of plant and controller processes. The plant is further defined by

$$plant = arm \|sensors\|$$

actuators

where

$$sensors = positionSensors \|forceSensor\|tactileSensor\|Camera$$

and

$$actuators = gripper \| joystick \| keyboard$$

The model of the plant will have to represent certain timing constraints. The camera works at 30 Hz, and the force sensor at 400Hz. The robot and position sensors work at 1000Hz, the joystick at 25Hz, and the tactile sensor at 120Hz.

The required specifications are: design a controller that will enable a user to manipulate the arm to perform various tasks at certain speeds, e.g. welding a part to an auto on the assembly line. The sensor measurements must be scanned at the correct rate. The actuators must be activated at the correct time. If an unfamiliar obstacle is encountered stop the arm movement within one second.

The specification S of required behaviour so far only refers to elements of the plant such as the arm, the sensors and actuators. The controller must still be designed, and so its constituent parts cannot yet be referred to in the top level specification.

Having specified as precisely as possible the plant, and the specification S that it must satisfy, the controller must now be designed. It was necessary to structure the description of the plant with the parallel composition operator. So too, it is often also necessary to structure the controller description.

contributors Duncan Thomson and David Stewart

### 2 DEFINING THE TERMS

For example, it is possible that only some of the sensors will be used at any one time. A logical way to separate the control functions is by having one task supervise the control signals to the robot and another task read the camera. Other distinct tasks can read the position and force sensors. If only the force sensor is needed for a particular task, and not the camera, then it is simply a matter of starting up the appropriate tasks without the need to change any code.

Without concurrency the software must be constructed as a single control loop called a cyclic executive. Such a large sequential program with multiple conditional flags such as "if (using camera) do action" is difficult to design robustly because of the different time frames and functions that must be accommodated. The structure of this loop cannot retain the logical distinction between controller modules. It is difficult to ensure that the executive synchronizes in a timely fashion with the plant processes, without the explicit notion of concurrent tasks in the controller software.

In a concurrent controller, each time frame is handled by a different task. The frequency of each task can be specified separately, and the burden of deciding what to run when is placed on the operating system scheduler. Even if the timing changes, there is no need to reprogram the controller. The real-time operating system is designed so as to be capable of adapting to the new requirements. If a large sequential program is used, the entire program would have to be restructured to satisfy the new timing requirements.

The use of concurrency is not without cost. There must be a run time support system to manage execution of controller tasks or processes. Such run time schedulers are often not considered in formal verification methods, but should be for a complete treatment of all system issues. Scheduling is treated as one discipline and verification as a different one. Methods that treat, in a unified framework, all aspects of verification and scheduling have not been sufficiently developed.

There is one part of the design process that is informal and intuitive. When the real world (e.g. of valves, pumps, vehicles, and robot arms) is translated into a formal mathematical model *plant* (e.g. of states, events and time bounds), there is no guarantee that the mathematical model properly represents the actual objects to be controlled. Similarly, there is no guarantee that the model *controller* is an accurate representation of all important facets of the actually implemented software (together with the hardware, CPU and run time system). This translation of real world objects into mathematical entities is by its very nature informal and intuitive.

As more experience is gained with a particular formalism, and actual designs based on the formal methods are experimentally checked in the field, so the formalism will gain more credibility. This is no different from the methods used in related disciplines. For example, a civil engineer will model the real world of bridges, beams and winds using the formal techniques of Newtonian physics. As more bridges are built and actually succeed in practice, so the Newtonian models gain credibility.

In certain cases, the pure Newtonian model must be adjusted with "safety factors" to account for the approximate nature of the models used. It is not clear what the software equivalent of safety factors is.

The fact that one part of the design procedure remains informal and experimental does not in any way detract from the need to use formal design procedures in the rest of the design. Just as the civil engineer uses formal Newtonian models for bridge building, and thereby increases confidence in the design, so too the designer of software uses formal methods to increase confidence in the correctness of the real-time system design. A proof of correctness is always relative to the formal models and specifications provided.

### 2.1 Major issues that formal theories must address

Formal methods for real-time systems must address the following problems:

- **Modelling:** Select appropriate models and formal notations for adequately describing plants and controllers. These notations must deal with the dynamic and reactive nature of the plants, and allow for the proper expression of timing properties.

- **Verification:** The verifier is presented with a formal mathematical model SUD where  $SUD = plant \| controller$ , and a specification S of how the plant should behave. The verification problem involves demonstrating that SUD satisfies the specification S.

- **Development:** In controller *development* a specification S is given that the *plant* must satisfy (the *controller* is not given). A disciplined method is sought whereby designers can be helped to construct a

controller so that SUD satisfies S. In development the controller should be built in a modularly structured compositional fashion ("controller architecture").

Synthesis: If controller development is fully automated, then it is called controller *synthesis*.

There are a few surveys in the literature of formal methods for realtime systems design [60,22,133]. This survey uses syntactic categories to classify the various formalisms. There are three main directions that must be distinguished, arranged by increasing formality and hence abstractness of approach. The first category to be dealt with is real-time languages. Then formalisms with visual specification languages are treated. Finally logics and algebras are discussed.

# 3 Real-Time Programming Languages

Modern real-time languages such as Ada [139], Chill [18], Occam [76] and Conic [65,79] typically have delay and timeout features for implementing timing constraints. In addition, these languages incorporate features such as task decomposition, abstraction (information hiding), communication and concurrency mechanisms that simplify the description of complex controller software.

For example, in Ada, a module can be decomposed into several tasks. A task can be further divided into two parts: the task specification and the body of the task. During initial program development, only the specification part of the tasks needs to be defined. The specification parts can be compiled to check for overall controller consistency. Later, the task bodies can be specified in more detail. The specification part is done by senior designers, because the specification represents the interface between software components. An error in such code may therefore have more serious ramifications than an error within a task body. A task can then be given to a junior programmer for coding.

Conic implements several useful reconfiguration primitives. The primitives allow for dynamic insertion or deletion of tasks or modules, while the rest of the system continues to run. Thus maintenance to controller software can be implemented without shutting down the plant. Occam has been used as a target language for process algebras (see Section 5.2).

The advantage of these languages is that at the end of the design process, the controller is available in directly executable code. However, most real-time programming languages lack an underlying abstract mathematical model. As a result the precise semantics is unspecified or even uncertain, and there is a proliferation of irrelevant detail not needed at the level of abstract specification. Usually the code must be converted into a formal notation (e.g. Petri Nets) before the code can be verified. If these languages alone are used, then the plant is not usually represented, although pseudo plant processes can be coded. Thus there is no method to formally verify whether the controller satisfies the requirements specification S.

# 4 Structured Methods and/or Graphical Languages

## 4.1 Structured Methods

Structured methods for real-time systems [44,141] originated in systems analysis methods used in industry starting a decade ago. These methods provide a structured set of system (read: controller) requirements. The system requirements specify what problem the controller must solve, and how the controller must be structured.

The system requirements includes various views and layers of the controller such as (a) data flow diagrams to decompose the controller, its functions and its flow of data, (b) control flow diagrams (enhanced state transition diagrams) to represent the system dynamics, (c) a requirements dictionary which is an alphabetical listing of all inputs, outputs, data and control flows, and (d) a table of response times in which the incoming and outgoing events (from and to the plant) are listed with their respective repetition rates or response times. The timing requirements are not particularly well integrated with the rest of the requirements.

These methods have been used with some success in actual industrial applications. However, these methods have no formal semantics. The resulting controller design cannot be executed for simulated behaviour, nor can they be compiled into code (e.g. into Ada or C). There is no support for formal verification. Nondeterministic plant behaviour cannot be suitably modelled.

## 4.2 Graphical Languages with a formally defined semantics

### 4.2.1 Statecharts and synchronous languages:

Statecharts [38] represents an improved version of the structured methods. A graphic tool called "Statemate" [41] exists to implement the formalism. Methods similar to that of Statecharts may be found in [29].

In Statecharts, the normal state transition diagram is enhanced with hierarchical and compositional features. For example, states can be clustered into super-states with the possibility of "zooming in" and "zooming out" of states. In AND decomposition, states are split into orthogonal (concurrent) subcomponents that communicate via broadcasting. OR decomposition decomposes a state into sub-states such that control resides in exactly one sub-state.

Statemate is formally based on a precisely defined (although rather complex) semantics. As an important consequence, there is an automated simulation tool which allows the user to execute the model. Exhaustive checking of all possible behaviours (for small systems) is supported. Models (e.g. of the controller) can be compiled into a target environment, although this tool is not yet fully developed. Formal verification is not yet supported, nor are time constraints treated in sufficient detail.

According to [86], the real-time aspects of Statecharts semantics is underdeveloped. A notation is needed for periodic timing functions, and for the specification of timing exceptions without the need to introduce additional states.

Recently, some progress has been made in providing formal analysis techniques for Statecharts. A fully abstract compositional semantics of Statecharts has been presented [53].

The simplest kind of semantics uses the operational notion of the set of all observable behaviours of a program or system. A behaviour may be defined as an infinite sequence of states that the system computes in one run. Such an operational semantics cannot usually be used to deliver a compositional (modular) semantics. In a compositional semantics, a compound system  $M_1 || M_2$  is described in terms of the semantics of the component systems  $M_1$  and  $M_2$ . A fully abstract semantics defines the behaviour of the system in sufficient detail without violating the principle of compositionality, i.e. such a semantics does not distinguish between more systems than is necessary to provide a compositional semantics.

The importance of compositionality is that structured program verification can be undertaken. Components of the system can be checked independently, and then combined to provide a verifiably correct compound program.

In addition to the abstract semantics of Statecharts presented in [53], there is an alternative version of Statecraft semantics. In [119], a semantics is presented that uses micro and macro-steps. Observable macro-steps are decomposed into a number of micro-steps. If event A triggers B then these events occur in subsequent micro-steps within the same macro-step. Thus a chain of causality inside one macro-step is modelled by a sequence of micro-steps. This avoids some of the causal paradoxes that occur in synchronous languages such as Statecharts.

The "synchrony hypothesis" assumes that a program instantly reacts to external events. In practice this means that the reaction time of the controller is always shorter than the minimum delay separating two successive external events in the plant. In addition to Statecharts, the languages Esterel [11], Signal [9] and Lustre [16] have been designed with the synchrony hypothesis in mind. The synchrony hypothesis must be applied with care as it can lead to causal paradoxes such as events disabling their own cause. This hypothesis is not always realistic, as the plant usually involves spontaneous behaviour that may occur at any moment of time. Languages such as Esterel do not allow for nondeterminism which is also not realistic for representing plants.

### 4.2.2 Petri Nets

Petri Net theory [116,129] was one of the first formalisms to deal with concurrency, nondeterminism and causal connections between events. According to [91] it was the first unified theory, with levels of abstraction, in which to describe and analyze all aspects of the computer in the context of its environment (computer + program + aircraft). Such a method must perforce contain a theory of concurrency, because of the three ingredients,

at most one — the program — is sequential. Previously the various components of the total system had to be described in diverse and unrelated ways. The computer hardware would be described by low level automata theories, the program by code in a sequential programming language, and the interaction of the program with its environment by narrative prose.

The classic Petri Net model is a 5-tuple (P, T, I, O, M). P is a finite set of places (often drawn as circles) representing conditions. T is a finite set of transitions (often drawn as bars) representing events. I and O are sets of input and output functions mapping transitions to bags of places (the incidence functions). M is the set of initial markings.

Places may contain zero or more tokens (often drawn as black circles). A marking (or state) of the Petri Nets is the distribution of tokens at a moment in time (i.e.  $M: P \to N$  where N is the nonnegative integers). Tokens in Petri Nets model dynamic behaviour of systems. Markings change during execution of the Petri Nets as the tokens "travel" through the net (modelling flow of materials for example).

The execution of the Petri Nets is controlled by the number and distribution of the tokens (the "state"). A transition is enabled if each of its input places contains at least as many tokens as there exists arcs from that place to the transition. When a transition is enabled it may fire. When a transition fires, all enabling tokens are removed from its input places, and a token is deposited in each of its output places.

Given an initial state (distribution of tokens), the reachability set is the set of all states that result from executing the Petri Net. Properties such as boundedness, liveness, safety and freedom from deadlock can be checked by analyzing the reachability graph. The reachability graph is usually constructed using an interleaving operational semantics.

Boundedness means that the number of tokens which any place in the net can accumulate is bounded. Boundedness implies that the system is finite state. In a Petri Net, a transition is said to be *live* if it is potentially fireable in all reachable markings. Liveness in the program verification sense is a different concept meaning that the transition must eventually occur.

In Petri Nets causal dependencies and independencies in some set of events are explicitly represented. It is therefore easy to provide a nonrestrictive partial order semantics. Events which are independent of each other are not projected onto a linear timescale. Instead a non-interleaving partial order relation of concurrency is introduced. In an interleaved execution, one cannot differentiate whether two events occur one after the other because the first is a prerequisite of the second, or whether this order in time is solely by chance [129].

There are also some structural analysis techniques that use linear algebra to check for invariants. Every marking can be represented as a vector, and the Net can therefore be modelled as a set of linear algebraic equations. An example of an invariant is a place-invariant, in which every place in the Net is assigned a weight, so that the weighted token count remains constant during the execution of the Net. The dual of the place-invariant is the transition-invariant. Since invariants are the characteristic solutions of the net equations, it is possible to compute them by well known techniques in linear algebra. These invariants are useful in the analysis of net liveness properties or of facts (propositional formulas that are true in all cases).

For large nets it is hard to compute the invariants. Usually, there are infinitely many invariants (a linear combination of invariants is also an invariant). Therefore it is often difficult to obtain the interesting ones. If the user supplies the invariant, it is somewhat easier to check automatically that the invariant holds true. If it does not hold, it is relatively easy to see where the net or the invariant must be modified.

Generic "health" checks such as the absence of deadlock can be performed. Such checks are not always useful as some kinds of deadlock may be allowed (e.g. program termination).

Controllers are specified by augmenting the plant Net with additional places and transitions to model the required controlled behaviour. For example, let the plant be a Petri Net *elevator*, and suppose it is required that the elevator be allowed to be disabled for possible maintenance work. A new place must be added to *elevator*, representing the emergency stop request. A new transition, representing the stop event, is also inserted into the net. The stop event is connected to the place in *elevator* that controls the elevator movement. Short of introducing a specification logic, there is no way (other than by modifying the details of the Net) to specify the abstract requirement that "if the stop event is requested then the elevator must eventually come to a halt and be disabled".

Ordinary Petri Nets have been criticized for not being able to deal with fairness and data structures (e.g. the data in a measure header) [62,94], although the number of tokens at a particular place in the net can simulate a local program variable. Structuring mechanisms such as composition operators are not inherently part of the theory, and there is no calculus to transform a net into a real-time programming language. Unlike state machines, a "place" in a Petri Net cannot easily be identified with a place in the corresponding program code. A further problem is that the reachability graph suffers from state explosion as Petri Nets become larger, thus impacting on the ability to scale up analysis to larger systems.

Ordinary Petri Nets are still an object of intense research aimed at putting Petri Net theory on firm mathematical grounds. However, practically speaking such standard nets are not up to the task of modelling complex systems. For this reason, higher level nets (coloured nets) and stochastic nets have been introduced to extend the modelling power of Petri Nets [13].

In coloured nets, the main idea is that the tokens themselves may have values (or colours). Coloured Nets allow for a more concise manageable representation of systems. They can be used to model data and resources that reside in the system. As long as the number of colours is finite, a Coloured Net is equivalent to a (much larger) ordinary Petri Net. An infinite number of colours allow for the expressive power of Turing machines so that most general questions become undecidable.

Petri Net theory was one of the first concurrent formalisms to deal with real-time. Two basic timed versions of Petri Nets have been introduced: time Petri Nets [88] and timed Petri Nets [124]. Both have been used in recent work [145,125,87,72,12,27]. There are two questions that arise when time is introduced to net theory: (a) the location of the time delays (at places or at transitions), and (b) the type of the delay (fixed delays, intervals or stochastic delays) [140].

Timed Petri Nets are derived from classical Petri Nets by associating a firing finite duration (a delay) with each transition of the net. The transition is disabled from occurring for the delay period, but is fired immediately after becoming enabled. These nets are used mainly in performance evaluation.

Time Petri Nets (TPNs) are more general than timed Petri Nets. A timed Petri net can be simulated by a TPN, but not vice versa. Both a lower and an upper bound are associated with each transition in a TPN. A state in the reachability graph is a tuple consisting of a marking, and a vector of possible firing intervals of enabled transitions in that marking. Since transitions may fire at any time in the allowed interval, states in the reachability graphs may have an unbounded number of successors (if continuous time is used). This adds complexity to the next-state function. Various techniques such as state classes and enumerative analysis techniques [12] have been introduced to overcome this problem. There are no necessary and sufficient conditions for boundedness (finiteness of the reachability graph); however, some sufficient conditions have been provided.

Perhaps the most general Petri Nets available for real-time problems are the ITCPN (interval timed colour Petri Net) models of [140]. These nets are higher level nets, and an interval is used to specify the timing characteristics, by attaching a timestamp to every token. The resulting semantics is quite elegant because both the timing and the colour are attributes of tokens. A software tool called *ExSpect* is available for performing analyses on ITCPNs.

In [72], safety properties of TPNs are analyzed without the need to necessarily generate the entire reachability graph. The idea is to work backwards from high-risk states to determine if these hazardous states are reachable. This backward method uses the inverse Petri net (reversed input and output functions), and is practical only when a small number of unsafe states is considered. The idea is to work backwards from unsafe states to all critical states (i.e. states having at least two successors). When a critical state is reached, interlocks can be used to force the system to take those paths that do not lead to unsafe states.

A similar backward method is employed in the real-time temporal logic approach to controller design in [103,107] (see Section 5.1.1). Instead of dealing with unsafe states one at a time, a predicate (characterizing a possibly infinite set of unsafe states) is used. Weakest preconditions are used to work backwards to critical predicates. The advantage of using predicates (rather than individual states) is that much larger systems can be treated. The method has been semi-automated. The backward method is an example in which the same basic idea is applicable in two very different computational models.

# 5 Logics and Algebras

Logics and algebras provide the most abstract approach to the analysis of real-time systems. These approaches typically consist of several elements. One element is a high level, formal specification language in which the requirements that the system must satisfy can be specified. A second element is a proof system (or finite state decision procedures) in which the correctness of the system relative to the specification can be verified. Another important element (that is not always provided) is a set of heuristics and general guidelines for using the approach on systems larger than the standard "textbook" examples.

Some researchers have investigated the general properties that any specification formalism must satisfy [55]. This is in contrast to the development of specific frameworks for doing verification. In [114], the relations that must hold between plant (environmental) variables and controller (software) variables are specified. These relations are used to express under what conditions a design is feasible, and what formal functional or relational properties a software requirements document must satisfy.

The current rigorous approaches to real-time systems are:

- Real-Time Temporal Logics,

- Algebraic Approaches (process algebras),

- RTL (Real-Time Logic) and Event/Action Models, and

- Assertional calculi

In this survey, a syntactic classification has been used based on the style of specification. The same underlying semantic model may often be applied to different syntactic specification styles. For example, both process algebras and temporal logics may be endowed with a discrete time semantics. Alternatively, in each case, a dense time semantics may be chosen. The classification of formal approaches could also have been performed on the basis of semantic models rather than syntactic specification styles.

There are a variety of timed transition systems (e.g. the timed automata discussed in [77]) that are being promoted as general models of real-time systems. These timed transition systems are not discussed in this survey as an independent group, but are treated individually where they relate to a particular specification language.

Some of the specification approaches are complementary. For example, temporal logic is good at describing properties that pertain to the complete system such as safety, liveness, fairness, and real-time response. However, temporal logic specifications are relatively unstructured, and could benefit from the more structured notions of processes algebras [22]. Process algebras are not good at specifying inherently global properties such as fairness which involve the complete computation. There is currently no theory that combines the best features of each formalism.

The following areas of research are listed below for the sake of completeness. They do not at present deal with real-time issues. However, they may be extended in the future to deal with real-time constraints.

- VDM [59] and Z [136] are specification languages based on set theory and predicate logic. These methods have been found useful for specifying large commercial systems [36], but are weak in their ability to deal with concurrency and real-time. They use concepts from classical programming logics such as Hoare's triples [49], and Dijkstra's weakest precondition calculus [23,35]. In [113], the first extension of Hoare triples to concurrent systems was provided.

- Control theoretic approaches based on algebraic methods and formal language theory have been developed for complex discrete event dynamic systems [123,122,54,15,75]. These methods are good at modular synthesis of controllers. They have on the whole not yet been extended to deal with real-time constraints, nor do they deal with data structures. Also noteworthy are the synthesis methods proposed in [84,24], and the automata based methods of [80,1].

- UNITY [19] is a specification and verification framework that uses extended state-transition systems to model plants and controllers (abstract programs). A logic, which is similar to temporal logic (but simpler), is used for specification and verification. A UNITY program describes what should be done. A mapping to a particular architecture is concerned with implementation details such as the type of machine that should be used. For example, the same abstract program can be mapped to a set of concurrent processors, to a single CPU using multiprogramming, or to a systolic array. This leads to a separation of concerns. Correctness is concerned with verifying the abstract program. Complexity is computed from the mapping to an implementation.

### 5.1 Real-Time Temporal Logic

The following discussion is taken from [104]. Temporal logic has its origins in philosophy, where it was used to analyze the structure or topology of time [130]. In recent years, it has found application in computer science, especially in the areas of software verification and knowledge-based systems [30,117,70,112,69,67,28,66].

In physics and mathematics, time has traditionally been represented as just another variable. First order predicate calculus is used to reason about expressions containing the time variable, and there is thus apparently no need for a special *temporal* logic.

Philosophers found it useful to introduce special temporal operators, such as  $\Box$  (henceforth) and  $\diamond$  (eventually), for the analysis of temporal connectives in language. The new formalism was soon seen as a potentially valuable tool for analyzing the topology of time. For example, various types of semantics can be given to the temporal operators depending on whether time is linear, parallel or branching. Another question that may be asked is whether time is discrete or continuous.

The temporal operators have been found useful for specifying program behaviour. A *structure* of states (e.g. a sequence or tree of states) is the key concept that makes temporal logic suitable for program specification. A formula, containing temporal logic operators, is interpreted over a structure of states.

In programming languages, the structures represent the computations executed by a program. Such a computation may be used to interpret a temporal formula. In this way, a programming language is said to be endowed with a temporal semantics.

Some of the different types of temporal semantics include:

- Interval semantics [134,95,96]. The semantics is based on intervals of time, thought of as representing finite chunks of system behaviour. An interval may be divided into two contiguous subintervals, thus leading to the *chop* operator.

- *Point semantics*, in which temporal formulas are interpreted as requiring some system behaviour with respect to a certain reference point in time. *Past* operators refer to the time prior to the reference point. *Future* operators refer to the time after the reference point.

Obviously, a point cannot be divided, and there is thus no simple definition of a chop operator.

Point semantics may be further divided<sup>2</sup> into three classes.

- Linear semantics [83,120,81]. In linear semantics, each moment has only one possible future corresponding to the history of the development of the system.

- Branching semantics [25,20]. In branching time semantics, time has a tree-like nature in which, at each instant, time may split into alternative courses representing different choices made by a system.

- Partial order semantics. Partial order semantics has been explored only recently. The reader is referred to [81] and other articles in the same volume as [81] for further information.

Once the type of *structure* to be used for interpreting temporal formulas is selected, there is still a further decision to be made. How are the structures to represent program executions or computations? There are at least two possibilities.

- Maximal parallelism [52,62]. The number of instructions in concurrent processes that can be executed simultaneously is maximized. Thus, two processes are never both waiting to achieve a shared communication.

- Interleaved executions. Concurrent activity of two parallel processes is represented by interleaving their atomic actions [82]. Fairness and time bound constraints are then used to exclude inappropriate interleavings (e.g. a sequence in which an enabled action is never executed).

The various temporal logics can be used to reason about *qualitative* temporal properties. Safety properties that can be specified include mutual exclusion and absence of deadlock. Liveness properties include termination and responsiveness. Fairness properties include scheduling a given

$<sup>^{2}</sup>$ Ron Koymans has pointed out [61] that interval semantics may also be coupled with linear/branching/partial orders — in practice interval semantics have tended to use linear time orders. However, in theory these are orthogonal issues.

process infinitely often, or requiring that a continuously enabled transition ultimately fire.

Various proof systems and decision procedures for finite state systems can be used to check the correctness of a program or system.

In real-time temporal logics, *quantitative* properties can also be expressed such as periodicity, real-time response (deadlines), and delays. Early approaches to real-time temporal logics were reported in [10,63,111]. Since then, real-time temporal logics have been explored in great detail.

### 5.1.1 The TTM/RTTL framework — explicit clock linear logics

The TTM/RTTL framework was first presented in [111], and in detail in [102]. It includes the following elements: (a) a semantic model of time, (b) a generic computational model (Timed Transition Models<sup>3</sup>) for modelling plants and controllers, (c) an abstract specification language (Real-Time Temporal Logic), (d) verification methodologies including model-checking for finite state systems, and a deductive proof system for infinite state systems, and (e) heuristics for constructing proofs and controller synthesis methods [104,105,110,107,109,108]. The first four elements represent an extension of untimed Manna-Pnueli temporal logic [82] to timed systems. Each of these elements is discussed below.

Semantic model of time: The notion of a possible behaviour or trajectory  $\sigma$  of a system is given by an infinite sequence of states  $q_i$  and events  $\tau_i$  defined as

$$\sigma \stackrel{\text{def}}{=} q_0 \stackrel{\tau_0}{\to} q_1 \stackrel{\tau_1}{\to} q_2 \cdots \stackrel{\tau_{i-1}}{\to} q_i \stackrel{\tau_i}{\to}$$

representing a possible run or computation of the system.

A discrete notion of time is employed using an external (conceptual) explicit clock. There is a distinguished tick transition, corresponding to the movement of the clock whose current time is represented by the variable t, with type(t) (the set of all values that t can have) the nonnegative integers. The clock event tick occurs infinitely often ("time must make progress") in the trajectory  $\sigma$ . When the clock tick occurs it increments t by one ("time never decreases"). No event other than the clock tick can change the time. The clock ticks are interleaved with other system transitions.

<sup>&</sup>lt;sup>3</sup>Originally called Extended State Machines.

### 5 LOGICS AND ALGEBRAS

Time bounds on events determine when they may occur relative to the clock ticks. A lower time bound l on the event  $\tau$  means that it may not occur prior to l ticks of the clock. An upper time bound u means that  $\tau$  must occur no later than u ticks of the clock (unless  $\tau$  is preempted by some other event). Thus an event that is continuously enabled over an interval of time does not actually occur for l ticks of the clock, but must occur by u ticks of the clock or become disabled.

Many events may occur between two ticks of the clock, in which case the events can only by distinguished by temporal ordering, not by time. A discrete time domain necessarily sacrifices information about precise times.

A computational model: Timed Transition Models (TTMs) provide an effective representation of realizable systems. Concrete real-time programming languages, Petri Nets and Statecharts can be mapped into TTMs. Most real-time features such as delays, timeouts and various scheduling constraints can be represented. True parallel processing, multiprogramming, communication through shared variables as well as message passing over channels can also be modelled.

A TTM M is defined as a 3-tuple  $M = (\mathcal{V}, \Theta, \mathcal{T})$ , where  $\mathcal{V}$  is the set of *activity*<sup>4</sup> and *data* variables (including the clock variable t).  $\Theta$  is a predicate asserting an initial condition on the variables.  $\mathcal{T}$  is the set of all transitions (representing events). Each transition has an enabling condition, transformation function, and lower and upper time bounds.

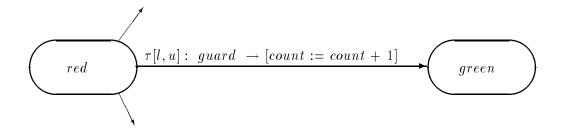

TTMs may be composed in parallel with each other to obtain more complex TTMs. A graphical language such as Statecharts is used to visually represent TTMs to the designer. The visual notation of Statecharts is extended by annotating each transition with its enabling condition, transformation function, and lower and upper time bounds.

For the transition

<sup>&</sup>lt;sup>4</sup>An activity variable is also sometimes called a *control* or *location* variable. An activity is any particular value that the activity variable may assume. The word "activity" is used rather than "state" as the word "state" is reserved for the global vector of all values of activity and data variables. An activity has persistence as opposed to a transition which occurs instantaneously.

the variable *count* is an example of a data variable that counts the number of times the traffic light has changed from the activity *red* to *green*. The intended operational meaning is as follows. The transition is said to be *enabled* if (a) the guard is true, and (b) the TTM currently resides in activity *red*. The lower time bound *l* guarantees that once  $\tau$  becomes enabled, then it may not occur for at least *l* ticks of the clock. Meanwhile, other enabled transitions may occur and disable  $\tau$ . After  $\tau$  has been continuously enabled for more than *l* ticks of the clock, then the transition  $\tau$ *may* be taken, instantaneously moving the TTM from red to the activity *green*, and simultaneously incrementing the counter by one. After having been continuously enabled for *u* ticks of the clock, either  $\tau$  *must* be taken before the next clock tick or be preempted by the occurrence of some other transition that disables  $\tau$ .

A spontaneous transition  $\tau[0,\infty]$  represents an event that may occur at any moment. However, it may also delay occurring forever. Spontaneous transitions are useful for modelling nondeterministic unpredictable behaviour in the plant. Examples include the failure of various devices (e.g. a pump or a valve). Spontaneous transitions can also representing situations where the designer initially has no knowledge of the time bounds.

More than one transition may be enabled and eligible (by virtue of its bounds) to occur at any point in time. In such a case, the order of transitions (in a behaviour) are chosen nondeterministically. This is typical of how the interleaving approach represents a process that must occur along several edges at the same time.

In [71], a set of transformations for taking a given TTM into a new TTM that is bisimulation equivalent is proposed. These transformations can be used to show that an implementation TTM is correct with respect to a specification TTM (in the style of process algebras discussed in the

### 5 LOGICS AND ALGEBRAS

next section).

**Concise specification language:** RTTL (real-time temporal logic) is used to specify the properties to be verified. Given the timed transition model  $SUD \stackrel{\text{def}}{=} plant \| controller$ , the objective is to check that SUD satisfies a specification S (which is a formula of RTTL).

An example of an RTTL formula is the *bounded response* time given by

$$\forall T[(red \land t = T) \to \Diamond (green \land T + 3 \le t \le T + 5)]$$

In the above formula, the clock variable t is a flexible variable. The quantified variable T is a rigid variable. The clock variable is called flexible because it changes from state to state in the trajectory. By contrast, the rigid variable T retains the same value over all states in the trajectory, and is used to record the time when red becomes true. Accordingly, the above formula asserts that if the traffic light is red at time T, then eventually within 3 to 5 ticks from T the light must turn green. The bounded response property may be *abbreviated* by the formula

$$red \rightarrow \diamondsuit_{[3,5]} green$$

RTTL is an *explicit clock* logic because an RTTL formula may explicitly use the clock time variable t with any of the arithmetic operators (e.g.  $+, -, =, \leq, >$ ), using arbitrary first order quantification over rigid time variables. Hence RTTL is very expressive but undecidable (see Section 5.1.2). RTTL may be used to: (a) refer to absolute times (e.g. "do some action on January 22nd 1998"), or (b) relate adjacent temporal contexts (e.g. "every stimulus A is followed by a response B, and then by another response C that is within 5 ticks of the original stimulus A").

Verification via model-checking and proof systems: The modelchecking<sup>5</sup> problem is as follows: check whether all legal trajectories of a finite state timed transition model SUD satisfy a specification S. The challenge is to construct a finite reachability graph, even though the time domain is unbounded.

<sup>&</sup>lt;sup>5</sup>The notion of model-checking was first explored by Clarke and others [20] in the context of (untimed) branching time temporal logics.

### 5 LOGICS AND ALGEBRAS

In [105,109], algorithms (and an implemented verifier) are provided for checking a subset of RTTL specifications. The verifier represents processes in a fashion close to the mathematical definition of TTMs. All kinds of data variables are treated including booleans, enumerated or numerical types, lists, sets and sequences. If an RTTL property fails to hold, then the failing trajectories are provided, making it possible to debug the system.

Model-checking suffers from exponential explosion in the size of the state space, when dealing with the parallel composition of processes. Modelchecking is suitable for checking small core parts of real-time systems. Reduced models, such as the synchronization skeleton of a mutual exclusion protocol, can also be treated. Large systems will often require different techniques.

For large systems (or infinite data domains) a deductive proof system must be used. A sound first order proof system for RTTL is presented in [104]. The proof system reduces to standard Manna-Pnueli temporal logic if all the upper and lower bounds are zero and infinity respectively.

An advantage of RTTL is that no new temporal operators are introduced. As a result, all the proof rules of Manna-Pnueli temporal logic can be used. In addition, certain rules are added for the real-time part of the reasoning [104,108]. Systems in which there are mixed fairness and time constraints can also be handled.

**Pragmatics** — **Semi-automated proof and synthesis methods:** A proof system, with perhaps some small examples to illustrate the method of proof, is not on its own sufficient to make the proof system practically useful for infinite state systems. Additional guidelines and heuristics must provide insight to the design and verification procedures. Automated support tools (beyond model checking for finite state systems) are needed. Theorem provers must be provided with adequate tacticals (built in heuristics) to support verification.

RTTL has heuristics for doing proofs using proof diagrams and weakestpreconditions [104,108]. A proof diagram is an abstract view of a state reachability graph. It is not confined to finite state systems because a node in the proof diagram is a predicate that can characterize a possibly infinite set of states. The proof diagram contains the intuition of system executions without the distracting proliferation of states. Most of the reasoning takes place in the ordinary predicate calculus, with temporal or real-time reasoning introduced only where absolutely needed.

Constraint logic programming has been used to semi-automate the heuristics. The language  $CLP(\Re)$  was used initially [106], but more recently the constraint logic language PrologIII [107] has been investigated for providing automated support. Methods of synthesizing controllers (for some infinite state systems) to satisfy given plant specifications are provided in [107] (see also the last paragraph of Section 4.2.2).

In [64], it is claimed that explicit clock logics such as RTTL do not "hide" time in accordance with the original philosophy of temporal logic (which was to abstract from time as much as possible). Specifications are not as succinct as hidden clock logics. However, most of the reasoning about time in RTTL involves the use of abbreviated formulas (similar to the bounded operators of hidden clock logic). Explicit time is resorted to only in those instances where needed (e.g. to refer to adjacent time contexts or other properties that hidden clock logics cannot specify).

It has also been claimed [56,62] that while the interleaving model of computation may be adequate for qualitative analysis of systems, a more realistic model such as maximal parallelism is needed for real-time systems. This claim is refuted by the interleaving model in the TTM/RTTL framework, in which system actions are interleaved with clock ticks. A careful incorporation of time allows for an adequate representation of most real-time phenomena while preserving the simplicity associated with interleaving models, namely, at any one point in time only one transition can occur and has to be analyzed.

The main disadvantage of the framework is its lack of compositional proof methods, although some of the synthesis methods allow for a modular style of controller development. The question of modular specification and verification methods is an active area of research in the field. Manna-Pnueli temporal logic has recently been provided with a compositional proof system [82]. Since RTTL is based on the untimed Manna-Pnueli system, it appears that their compositional methods should also carry over to RTTL.

The TTM/RTTL framework is a state-based, linear discrete time, interleaved, asynchronous, explicit clock logic formalism. It is state-based because states rather than actions are the primitive components of behaviours. State-based approaches may be more general than action based methods (e.g. process algebras) because state based methods can easily encode actions as well as histories of actions It is difficult to extract the state from action based formalisms.

TTM/RTTL uses a discrete time domain rather than a dense (e.g. the rationals) time domain. If simplicity of use can be preserved, the more general modelling powers of a dense time domain would be preferable. Concurrency is modelled by interleaving rather than a partial order or maximal parallelism. It is asynchronous because a finite number of events can occur between clock ticks. In a synchronous model, all concurrent activity happens in lock-step with the tick of the clock.

Many of the choices made in TTM/RTTL computational model are independent of each other. For example, RTTL can be defined over dense as well as continuous time domains. It can be given a branching time semantics or be based on time intervals. The choice of semantics is, in principle, independent of the syntax of the specification language [61,46]. The reader is referred to [118,46,47] for other explicit clock logics. In particular, [47] compares explicit clock logics with hidden clock logics.

### 5.1.2 MTL — hidden clock linear logics and other RTTL fragments

Metric Temporal Logic (MTL) [64] is a fragment of RTTL in which references to time are restricted to bounds on the temporal operators. For example, the formula  $A \rightarrow \bigotimes_{\leq 5} B$  means that if A occurs then eventually within 5 time units B must occur. No references to an explicit clock are allowed and hence MTL is called a *hidden clock* or *bounded temporal operator* logic.

Interpretations for MTL are metric point structures based on a linearly ordered time domain. A distance function provides a metric for time. Various time constraints can be imposed on the distance function, depending on the notion of time that is used (e.g. transitivity, irreflexibility, and the existence of absolute differences).

In the hidden clock approach,  $\diamond_{\leq 5}$  is a new temporal operator that restricts or bounds the scope of the qualitative operator  $\diamond$ . The bounded formula  $\diamond_{\leq 5} B$  predicts the occurrence of B within 5 time units from now. The qualitative formula  $\diamond B$  asserts that B will eventually happen, but puts no bound on when.

In [64], a real-valued time domain is used. This allows MTL to ex-

press certain properties of continuous time variables (e.g temperature and pressure) more succinctly than discrete time logics. MTL does not allow references to an absolute point in time, nor does it allow the specifier to relate adjacent temporal contexts. A sound proof system for MTL is provided.

An important extension to the literature on MTL is a compositional proof system for Occam style programs [52,50]. The proof system uses the maximal parallelism model of program execution. Because the proof system is compositional, the properties of a compound system  $P_1 || P_2$  (the parallel composition of two simpler processes  $P_1$  and  $P_2$ ) can be deduced from specifications of its constituent parts ( $P_1$  and  $P_2$ ), without any further information about the internal structure of these parts. Compositionality is important for scaling up the application of the proof system to deal with large systems in a structured fashion.

It is not clear whether the proof system can be extended to reason about complex plant descriptions, which are not always representable in Occam. The extra *chop* operator, needed for compositional proofs, makes the reasoning relatively complex. Nevertheless, once a module's specification is fixed, any implementation of the module with the same specification can be used, without having to redo the proof.

Alur and Henzinger [6] have compared various ways in which to restrict RTTL to obtain decidable fragments of the logic. These fragments are restricted to finite state, propositional temporal properties. There are at least four interesting syntactic fragments of RTTL:

- MTL [7,64] is a discrete time propositional version of the bounded operator logic discussed above.

- XCTL [43] is a discrete time propositional explicit clock logic. The atomic timing constraints allows the primitives of comparison and addition. XCTL restricts the quantification level. It allows only one outermost level of quantification over rigid time variables. The quantification is therefore never explicitly displayed. On the other hand, it allows general arithmetic timing expressions, including addition and subtraction of variables and constants.

- TPTL [7] is a discrete time propositional logic whose timing constraints allow comparison and addition (but only of integer constants,

i.e. no variables). TPTL uses auxiliary static timing variables to record the value of the clock at different states, but replaces the explicit references to the clock itself by a special type of freezing quantification.

• MITL [5] employs a dense time domain. It has a bounded-operator syntax, but cannot express punctuality properties. A *punctuality* property states that the event B follows A in *exactly* 3 seconds.

All of the above fragments can be interpreted over discrete, dense and continuous time domains. The fragments can then be compared for expressiveness, and complexity of satisfiability and model-checking.

Satisfiability is important in the homogeneous verification case. Let the implementation I and the specification S (that the implementation must satisfy) can both be given as temporal logic formulas  $F_I$  and  $F_S$  respectively, in the appropriate fragment of RTTL. Then the implementation I meets the specification S iff the implication  $F_I \rightarrow F_S$  is valid (or, equivalently, if the conjunction  $F_I \wedge \neg F_S$  is unsatisfiable). Only propositional versions of temporal logics are decidable for satisfiability. Decidability depends on the nature of the time domain (discrete, dense etc.) and the operations on the time domain that are permitted.

Model checking is important in the heterogenous verification case. The implementation I is given by a timed automaton or timed transition system [4,5]  $A_I$ . The specification S is given by a temporal logic formula  $F_S$ . To do the check, a timed automaton  $A_{\neg F_S}$  is constructed from the negation of the specification  $\neg F_S$ . The implementation I satisfies the specification S precisely when the product automaton  $A_{\neg F_S}$  has no run (timed observation sequence).

Let RTTL(<,s) denote the restriction of RTTL to propositions and timing constraints containing only ordering (<), successor(s), and congruence over time (e.g. all times with an even time difference from the initial state). Thus, RTTL(<,s) is interpreted over a discrete time domain, and can be used to specify constant lower and upper time bounds on the time distance between events. The various logics are compared in Table 1 for satisfiability, model checking and expressiveness over discrete and dense time domains relative to RTTL.

For any real-time logic that is closed under boolean operations, and that can express punctuality, the satisfiability problem is undecidable for

| Discrete Time              | Satisfiability    | Model Checking    | Expressiveness     |

|----------------------------|-------------------|-------------------|--------------------|

| RTTL                       | undecidable       | undecidable       |                    |

| $\operatorname{RTTL}(<,s)$ | nonelementary     | nonelementary     | $< \mathrm{RTTL}$  |

| XCTL                       | PSPACE-complete   | PSPACE-complete   | $< \mathrm{RTTL}$  |

| TPTL                       | EXPSPACE-complete | EXPSPACE-complete | =RTTL( $<$ ,s)     |

| MTL                        | EXPSPACE-complete | EXPSPACE-complete | =RTTL( $<$ ,s)     |

| MITL                       | EXPSPACE-complete | EXPSPACE-complete | $< \rm RTTL(<, s)$ |

| Dense Time                 | Satisfiability    | Model Checking    |                    |

| RTTL                       | undecidable       | undecidable       |                    |

| RTTL(<,s)                  | undecidable       | undecidable       |                    |

| XCTL                       | ?                 | ?                 |                    |

| TPTL                       | undecidable       | undecidable       |                    |

| MTL                        | undecidable       | undecidable       |                    |

| MITL                       | EXSPACE-complete  | EXPSPACE-complete |                    |

Table 1: Comparison of linear propositional real-time logics

a dense time domain. MITL cannot express punctuality properties, and is thus less expressive than the other logics, but remains decidable even if the time domain is dense.

In [43] it is shown that XCTL and TPTL/MTL are incomparable. For each of these logics, there is a property expressible in one which is not expressible in the other. Each of these properties is a reasonable realtime requirement. In the discrete time case, TPTL and MTL are equally expressive (it is conjectured that this equality does not extend to dense domains [46]).

There are doubly-exponential-time decision procedures for both TPTL and MTL. The verification algorithm for MTL depends, exponentially, on the value of the largest time constant involved. It is a little less expensive than the algorithm for TPTL, which depends exponentially on the value of the product of all time constants.

XCTL is not closed under negation, and hence cannot be used to solve the homogeneous verification problem. However, a special model-checking algorithm for XCTL has been given that is doubly exponential in the size of the specification formula and singly exponential in the size of the model.

### 5.1.3 Branching time temporal logics

Linear time and branching time logics are incomparable. For example, branching time logics cannot express general fairness constraints in the syntax of the language (although certain fairness conditions can be imposed by external constraints on the reachability graphs when doing model checking for example). Linear time logics can directly specify fairness. On the other hand, branching time logics can express certain existential path conditions (e.g. it is always possible for the system to eventually do some action). Such path constraints cannot generally be expressed in linear time logics.